国产EDA新突破 芯华章数字验证调试系统提供完善生态支持

2022年5月11日,EDA(集成电路设计工具)智能软件和系统领先企业芯华章正式发布基于创新架构的数字验证调试系统——昭晓Fusion DebugTM 。该系统基于芯华章自主开发的调试数据库和开放接口,可兼容产业现有解决方案,提供完善的生态支持,并具备易用性、高性能等特点,能够帮助工程师简化困难的调试任务,有效解决难度不断上升的设计和验证挑战。

在芯华章研讨会暨产品发布会上,芯华章科技软件研发总监黄世杰详细介绍了昭晓Fusion DebugTM产品的完整解决方案,并且用实际项目演示了工具的典型应用场景。合肥市微电子研究院院长陈军宁、电子科技大学电子科学与工程学院副教授黄乐天、中兴微电子有线系统部部长贺志强、平头哥上海半导体技术IP验证及软硬协同验证负责人张天放、燧原科技资深架构师鲍敏祺等行业专家与学者也受邀出席,共话半导体产业发展及验证EDA技术趋势。

谈及前端验证面临的挑战时,鲍敏祺表示:“一方面芯片验证场景日益复杂,从单纯的功能验证到今天面对整个系统级、场景级的验证;另一方面,面对激烈的市场竞争,芯片集成规模不断扩大,研发周期却不断缩短,验证的重要性日益突出。”

据了解,在典型的SoC芯片研发项目中,工程师通常需要花费四成左右的时间进行调试,工程复杂且费时费力。好的调试系统不仅可以确保项目的成功,更可以有效提高SoC芯片的设计和验证效率,降低芯片设计成本。

作为国内率先发布的数字验证调试系统,昭晓Fusion DebugTM 的发布填补了多项国产技术空白。相比于国际主流数字波形格式,芯华章的昭晓Fusion Debug TM 采用完全自研的高性能数字波形格式XEDB。该波形格式借助创新的数据格式和架构,具备高性能、高容量、高波形压缩比等特点,其提供的高效编码和压缩方案,在实际测试中可以带来比国际主流数字波形格式超8倍的压缩率。与其它商业波形格式相比,XEDB的读写速度快至3倍,并支持分布式架构,可充分利用多台机器的物理资源来提升整体系统的性能,实测中表现出的波形写入速度可以比单机模式提高5倍以上,这对复杂的软硬件协同验证与调试至关重要。

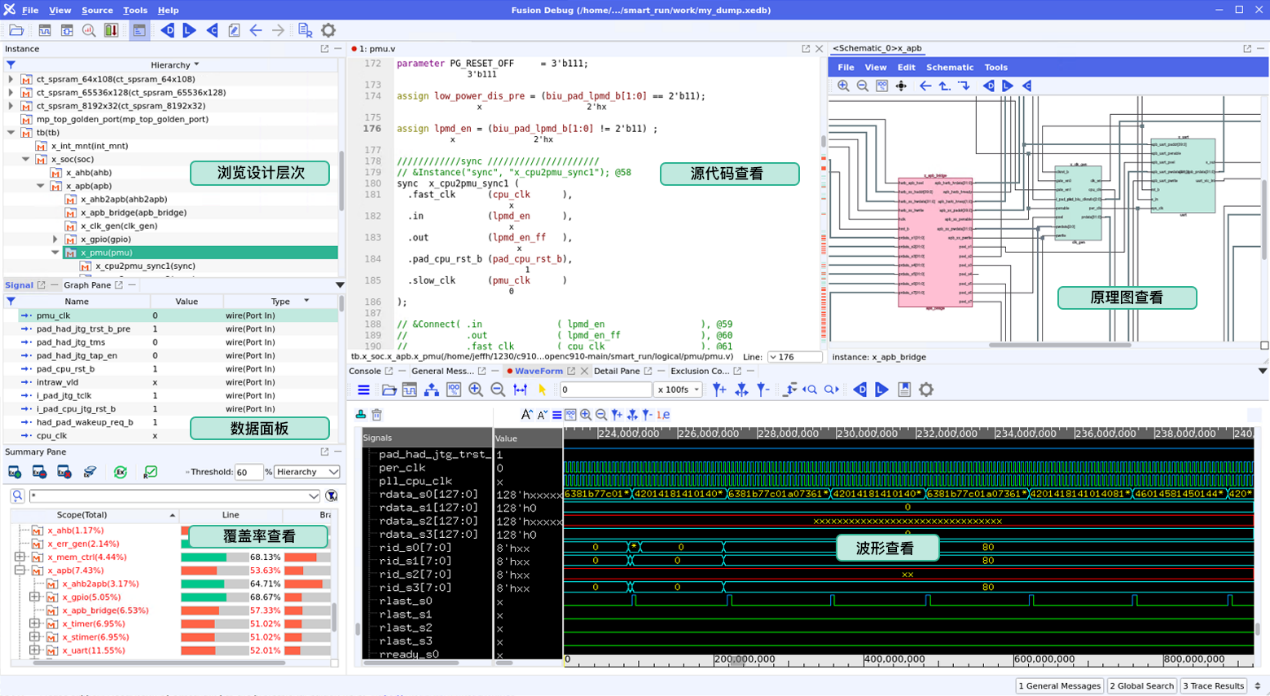

在提供完整调试解决方案的同时,昭晓Fusion DebugTM由创新的设计推理引擎和高性能分析引擎提供动力,能够支持统一且高性能的编译,快速加载仿真结果和信号显示,轻松进行信号连接跟踪和根本原因分析。根据实际项目数据显示,在完整的设计及原理图模块化加载中,昭晓Fusion Debug TM 的速度比其他商用EDA工具快至5倍,

能满足大规模SoC 设计调试的需求,并大大提高了验证效率,从而加速芯片设计创新。

Fusion DebugTM GUI界面

除了性能与效率上的突破,芯华章昭晓Fusion DebugTM 还针对行业实践痛点,提供了不同于一般调试工具的创新解决方案。

“在实际应用中,各个芯片的产品调试特征不同,对调试会产生非常多样化的细分需求。”张天放在谈到一般调试工具在应用中的挑战时表示,“我们希望能够在国产EDA工具里面看到一些开放的接口,便于进行二次开发。”

对此,芯华章科技首席市场战略官谢仲辉表示,“昭晓Fusion DebugTM提供丰富、可编程的数据接口,让用户可针对不同调试场景进行定制化,并能贯通芯华章智V验证平台及支持用户现有的EDA工具,为用户带来更加客户一体化的调试解决方案,从而提供更加普惠的生态支持和用户体验。”

近年来,芯片设计的规模越来越大,摩尔定律逐渐走向极限,芯片验证的难度也随之提高。在谈到下一代设计验证工具时,陈军宁与黄乐天均从不同角度指出,下一代EDA工具需要增强工具间的融合以及更智能化,在减少人力投入的同时,进一步充分利用机器学习、云计算等创新技术,从而提高芯片验证与设计效率。

贺志强也表示:“国产EDA公司拥有高技术起点和贴近本地市场的优势,能够基于客户的痛点进行开发,将经验与解决方案集成到工具当中。作为国产 IC企业,中兴是国产EDA工具天然的天使用户,我们会全力支持国产EDA的发展。”

芯华章科技研发副总裁林扬淳表示:“昭晓Fusion Debug TM融合了先进的机器学习框架,带来更高的验证效率和更智能化的操作体验,致力于解决当前产业调试方案缺乏创新、数据库碎片化以及性能局限等多重挑战,让芯片设计更简单、更高效。”

免责声明:市场有风险,选择需谨慎!此文仅供参考,不作买卖依据。

责任编辑:kj005

文章投诉热线:156 0057 2229 投诉邮箱:29132 36@qq.com