Chiplet Summit|Chiplet时代芯启源的探索之路

全球首届Chiplet峰会(ChipletSummit)于1月24日至26日在美国硅谷召开,芯启源受邀参加此次峰会同与会专家共同展望Chiplet时代的半导体产业趋势及挑战。

英特尔代工服务事业部(Intel Foundry Services)、开放计算项目(Open Compute Project)、应用材料公司(Applied Materials)等国际知名企业、项目及联盟的创始人和工程师出席本次峰会。

芯启源芯片执行副总裁JimFinnegan

26日,芯启源芯片执行副总裁JimFinnegan在峰会上进行了主旨演讲,内容涵盖:

推动Chiplet技术产生的背景;

对于DPU芯片这种本身设计复杂、软硬件需要协同设计验证的芯片,采用Chiplet技术会带来哪些实际挑战和障碍;

Chiplet技术在芯启源DPU芯片中的实际应用;

芯启源是如何通过采用MimicPro原型设计和仿真平台来解决Chiplet仿真面临的挑战。

推动Chiplet技术产生的背景

英特尔联合创始人Gordon Moore于1965年在《把更多组件放在集成电路上》(Cramming more components onto integrated circuits)中正式提出著名的摩尔定律的同时,还提出了Chiplet最初的概念模型,他指出“用较小的功能构建大型系统更为经济,这些功能是单独封装和相互连接的”。

随着Dennard缩放定律和Moore定律接近终结,依靠单颗die满足日益增长的功能和性能需求越来越不可行,这不仅仅体现在晶体管密度、功耗等等技术限制,从成本角度也越来越不可行,具体表现在:

1.单个晶体管成本在3Dfinfet时代不再呈现下降趋势

Source“Measuring Moore’s Law”, Kenneth Flamm, 17.Nov

2.随着单颗芯片集成功能越来越多,芯片面积越来越大,良率(yield)也会降低,导致单个晶体管成本上升

3.先进工艺的流片成本越来越高

延续摩尔定律经济效益:高速互联&异构集成

AMD较早地采用了Chiplet架构,并发现其优秀的性价比优势:

2021/6“AMD on Why Chiplets and Why now?”

Chiplet技术将原本一块复杂的SoC芯片分解为小的芯粒,其模块化设计的概念,将有利于架构设计的重新划分和创新,实现芯片的不同功能区解耦,有利于一些芯粒的复用,形成系列化产品,可实现低设计成本、低制造成本、高良率,并且缩短产品商用上市时间和后续产品的迭代周期。

与传统SoC相比,Chiplet将不同的小芯粒通过先进封装形成系统芯片,目前业内众多企业正在引入Chiplet技术。Chiplet技术的出现是产业链提高生产效率的必然选择,也是未来几年复杂soc的主要芯片设计形式。

芯启源DPU芯片采用先进的Chiplet技术

在芯启源最新的第四代智能网卡架构中,通过应用Chiplet技术,极大的提升了自有智能网卡的性能;同时通过支持与第三方芯片的Die-To-Die互联,还可以集成更多的特定专业领域的芯片。

在性能和功能丰富度有飞跃式提升外,其下一代智能网卡芯片NFP7000为芯启源的客户提供了更多业务场景的支持能力。通过Chiplet技术选择不同数量和类型的芯粒组合能够实现入门级、中端、高端三类SoC系列芯片:

入门级:1个I/O芯粒加一个processor芯粒;在PCIe侧,支持16对serdes、4个PCle控制器;网络侧支持4对serdes,支持4x25/100G,2x200G,1x400G网络;能够支持2个LPDDR接口。

中端:通过各2个I/O芯粒和processor芯粒互联,实现性能的成倍叠加。

高端:高端级SoC封装多达4个I/O芯粒和4个processor芯粒;PCle支持64个serdes,16个控制器;网络侧最多32个serdes;能够支持8个LPDDR4x/5接口。

多个小芯片(Chiplets)的扩展互联

通过DPU芯片的Chiplet技术能够完全覆盖25G到400G的各类接口需求,提供高性能网络和host接口,能以线速或网络中的可用速度解析、处理数据,不再需要为不同的细分市场做不同的mask设计,实现高灵活度、高性能、低成本的硅片重用,更好的适应应用场景的需求。

Chiplet芯片设计新生态

芯启源具有完全自主知识产权的DPU芯片,其内部结构主要包括硬件协处理器、流处理器、PCIe主机接口模块以及内外部高速缓存和内存接口组成。下一代NFP7000芯片则基于Chiplet技术,采用die-to-die互联统一标准UCIe,不仅支持芯启源芯粒的die-to-die互联封装,还能够实现异厂家多芯片异构集成。

对于Chiplet当前的发展情况,芯启源研发副总裁陈盈安在之前的会议中也回顾了在Marvell期间参与“MoChi”互连架构开发的经历,各家厂商在die-to-die互连技术上,正逐步从私有标准、私有协议走向开放标准和协议,正如如UCIe联盟的诞生。

随着行业开放标准建立,越来越多厂商可以参与到生态中来,未来的系统厂商概念将会是不同芯粒的集成。芯启源智能网卡架构采用灵活可编程架构以及Chiplet技术,具备高度的可扩展性,能够适用于多种产品形态及解决方案,结合所打造的DPU生态,提供了开放,可编程的应用生态。

Chiplet技术虽然有着上述优点,但同时在EDA工具链上面临着很多技术难题。比如在增加系统复杂性的同时加剧了对于仿真器功能和性能的挑战,对仿真加速器的可扩展规模及FPGA利用率提出了更高要求等。

芯启源在Chiplet仿真方面的性能、可扩展性、工程效率、生态系统开放性和安全性思考和实践,如何通过采用其MimicPro原型设计和仿真平台解决。

展望Chiplet对半导体产业链的影响,芯启源研发副总裁陈盈安此前畅想过Chiplet产业未来的商业模式:如RISC-V架构CPU可作为die单独提供,芯启源也可以将之集成到其DPU产品中,应用于某一商业场景。芯启源从创始之初就一直保持着一个开放的开源社区生态,希望能够与全行业共同推动Chiplet产业进步。

免责声明:市场有风险,选择需谨慎!此文仅供参考,不作买卖依据。

责任编辑:kj005

文章投诉热线:156 0057 2229 投诉邮箱:29132 36@qq.com春节红包封面大比拼,科技文化交相辉映,中国广电别具特色

SD-WAN是什么?详解三大优势及SD-WAN解决方案

打造操作系统“大生态” 筑牢数字经济底座 麒麟软件助推网信产业发展质效双提

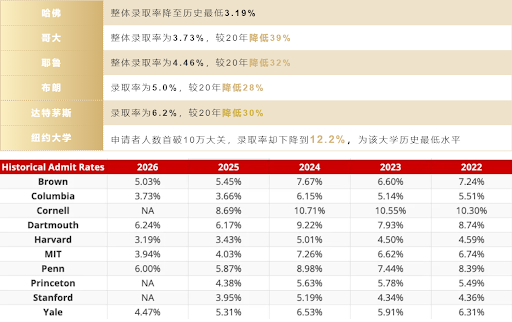

易美教育前斯坦福招生官因卓尼女士 深刻剖析创作藤校文书的黄金法则

第二届操作系统产业峰会将于1月9日盛大开幕 四大亮点抢先揭秘

中国广电2022盘点:让利于用户、5G网络下沉县乡,坚持差异化发展

相关新闻

最新资讯

2023年中概股上市回暖:宠医独角兽新瑞鹏赴美IPO,总收入同比增长26.9%

据悉,近日量子之歌(QSG)成功在纳斯达克(NASDAQ)上市,成为2023年首家登录美股的中国企业。仅2023年...